CANoe中关于NetworkHardwareConfiguration中的setup设置参数的详解

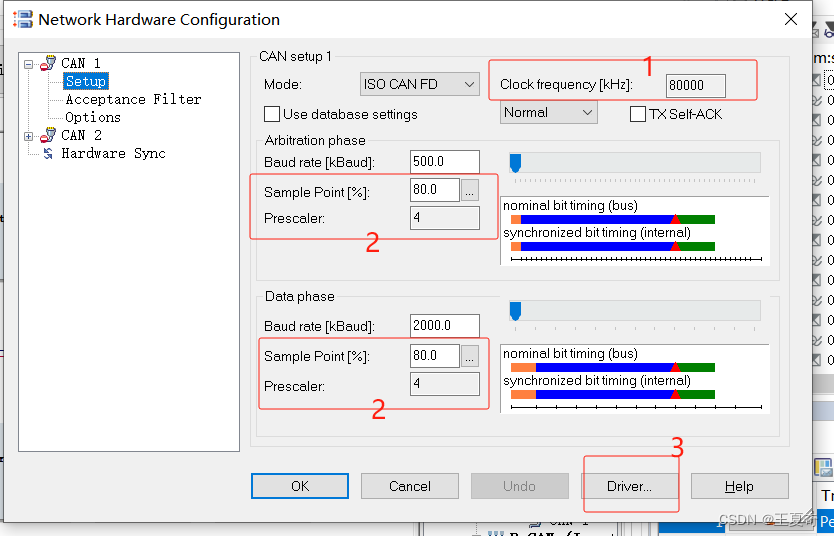

本文是以VN1640A中的CAN_FD工程为例,为大家讲解。1:首先打开相关配置重点讲解红色框中的参数,其他参数该如何设置,请参考我另外一篇文章“关于CANoe硬件及接口的学习笔记(VN1640A)”或自行查阅相关资料即可。

前提说明

本文是以VN1640A中的CAN_FD工程为例,为大家讲解。

1:首先打开相关配置

重点讲解红色框中的参数,其他参数该如何设置,请参考我另外一篇文章“关于CANoe硬件及接口的学习笔记(VN1640A)”或自行查阅相关资料即可。

1.1 ClockFrequency

这个值是对应VN1640A内部的晶振频率,为80000KHZ,是固定值。用户不可修改。

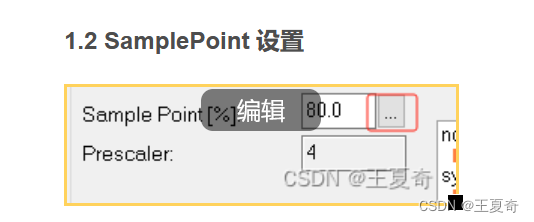

1.2 SamplePoint 设置

点击... 图标,进入以下界面

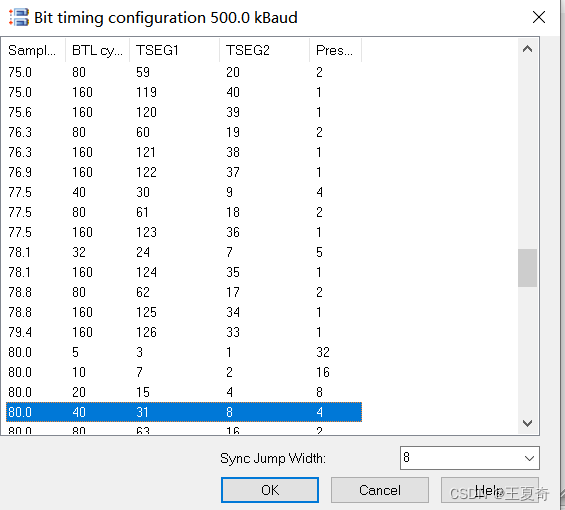

这张图中所有参数,都值得研究

**1)Sample point ,采样点,CAN中采样点,在结构上是有固定位置的,即位于TSG1与TSG2的交接点出(不了解的同学,可以查查关于CAN的再同步资料CAN的填充机制解释及其延伸知识_can总线 位填充-CSDN博客)

暂时我们还需要记住,Sample point采样点的取值范围= [50.6,96.3]

**2)BTL cycles:可以理解为将一个bit位,拆解为多少份,很多资料将拆解成的小份成为Tq。

BTL= (ClockFrequent/总线波特率)/PreScaler。

首先我们来了解一个概念(单片机中的概念),即一个单片机时钟的频率=X(单位频率),则它对应的震荡周期T=1/X。

单片机通讯中,又存在另外一个概念,即分频系数。

单片机时钟频率/分频系数=通讯波特率。

注意:但是CAN通讯中,又引用了另外一个概念,预分频(Prescrele),就是指一个Tq(最小时间单元)频率=单片机时钟频率/预分频系数。

我们看图中第一行

BTL =80 = (80000K/500K)/ prescaler ,prescaler=2 带入是不是就计算出来了。

BTL的选取规则,BTL将一个bit分解为BTL个Tq,总线下降沿的时间<=Tq的时间。

**3)TSG1,TSG2

CAN的再同步过程中将一个bit位分为三部分

SS(同步段,固定占一个Tq的时间)+TSG1+TSG2 =BTLcycle

采样点= (TSG1/BTL)*100%

**4)SJW(同步跳跃宽度)

SJW跳跃宽度的执行规则(重点)

CAN的位同步过程中:

1)当下降沿出现在TSG1中时,先观察下降沿出现在,距离SS与TSG1交界点处的距离,记为X个Tq的距离。当X<=SJW,时增加TSG1中X个Tq的长度。即可正常完成再同步。

2)当下降沿出现在TSG2中时,先观察下降沿出现在,距离TSG1与TSG2交界点处的距离,记为Y个Tq的距离。当Y<=SJW,时缩短TSG2中Y个Tq的长度。即可正常完成再同步。

大家回到,下图中的设置界面

带着以下问题,再去看一遍所有的配置选项

1:TSG2的数值和SJW的数值大小关系?。

2:上文我们有两个结论,(1)*TSG1和TSG2是根据SJW会动态变化,而TSG1又会根据SJW动态变长,TSG2又会动态变短。(2)sample point是在TSG1和TSG2的交界处的。那么是否能够说明Sample Point的点也是浮动变化的?

答1:TSG2=SJW,也就是说在再同步过程中,TSG1可以最大增加SJW个Tq的宽度。SJW=TSG2,也就说明甚至一个帧中TSG1可以完全覆盖TSG2。所以采样点的位置,应该这样描述更加准确,是在TSG1结束时刻。

答2:结论就是Sample Point的点也是浮动变化的。软件执行时只会根据TSG1结束作为采样执行的触发条件。

更多推荐

已为社区贡献5条内容

已为社区贡献5条内容

所有评论(0)